# Welcome to

#### Conference

January 28–30, 2025 Santa Clara Convention Center Ехро

January 29–30, 2025

JAN. 28–30, 2025

#DesignCon

### **SPEAKERS**

#### Zhiping Yang CEO, PCB Automation Inc. zhipingyang@pcbauto.ai

Zhiping Yang is the CEO of PCB Automation Inc. (<u>https://pcbauto.ai</u>) and an adjunct professor at Missouri S&T EMC laboratory. He worked in Waymo, Google, Apple, Cisco, and Nuova systems on automotive, consumer, and datacenter products. His research interests include signal integrity and power integrity methodology development for Die/Package/Board co-design, high-speed optical module, various high-speed cabling solutions, high-speed DRAM/storage technology, and high-speed serial signaling technology. He has published more than 70 research papers and 20 patents. His research and patents have been applied in Apple iPhone 5S/6/6S, Cisco UCS, Cisco Nexus 6K/4K/3K, and Cisco Cat6K products. He is actively involved with the IBIS Open Forum as a BoD member and officer. He is an IEEE Fellow and served the Technical Advisory Committee leadership roles in IEEE EMC society. He obtained his Ph.D. from University of Missouri-Rolla and his B.S. and M.S. from Tsinghua University, Beijing.

#### Ravi NarayaSwami, Design Engineering Group Director, Cadence rswami@cadence.com

Ravi NarayanaSwami is a Design Group Director in the Cadence Silicon Solutions Group with around 25 years of semiconductor development and systems engineering experience in Silicon Valley. His team's responsibilities include post-silicon tapeout activities to product validation related to high-speed SerDes and UCIe<sup>™</sup> subsystem IPs. He holds an M.S.E.E from the Florida Institute of Technology.

#DesignCon

## **UCle Overview**

#Des

### **Outline**

- UCle<sup>™</sup> Channel Compliance Overview

- 。 Eye Diagram Requirement

- Voltage Transfer Function (VTF)

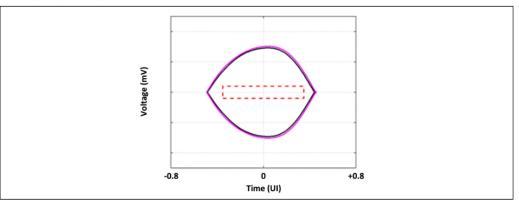

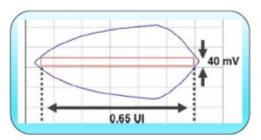

### Channel Spec: Eye Diagram Requirement\

#### Table 5-10. Eye requirements

| Data Rate<br>(GT/s)         | Eye Height<br>(mV) | Eye width<br>(UI) |

|-----------------------------|--------------------|-------------------|

| 4, 8, 12, 16 <sup>a c</sup> | 40                 | 0.75              |

| 24, 32 <sup>a b c</sup>     | 40                 | 0.65              |

a. Rectangular mask.

b. With equalization enabled.

c. Based on minimum Tx swing specification.

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

#DesignCon

(informa markets

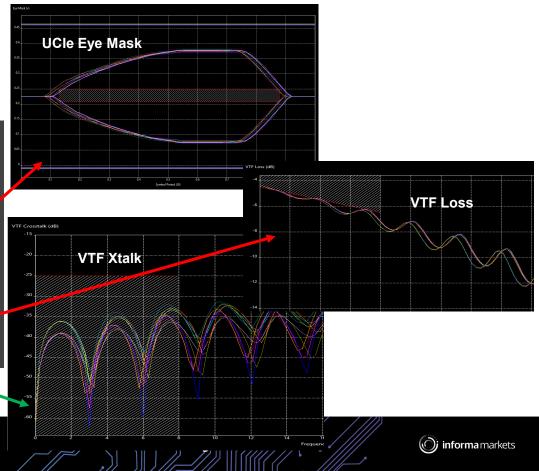

### **Channel Spec: Voltage Transfer Function**

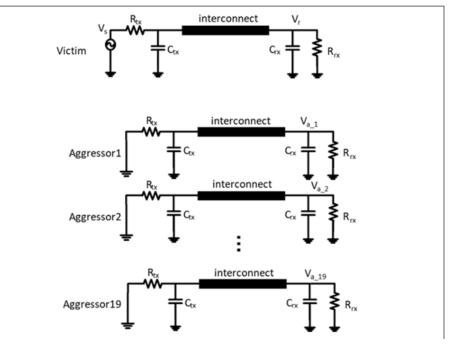

Figure 5-17. Circuit for VTF calculation

Voltage Transfer Function (VTF) based metrics are used to define insertion loss and crosstalk. VTF metrics incorporate both resistive and capacitive components of TX and RX terminations. Figure 5-17 shows the circuit diagram for VTF calculations.

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

#DesignCon

### **Channel Spec: VTF Loss**

VTF loss is defined as the ratio of the Receiver voltage and the Source voltage, as shown in Equation 5-1 and Equation 5-2.

Equation 5-1.

$$L(f) = 20\log 10 \left| \frac{V_r(f)}{V_s(f)} \right|$$

#### Equation 5-2.

$$L(0) = 20\log 10 \left(\frac{R_{rx}}{R_{tx} + R_{channel} + R_{rx}}\right)$$

L(f) is the frequency dependent loss and L(0) is the DC loss. For unterminated channel, L(0) is effectively 0.

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

#DesignCon

### **Channel Spec: VTF Crosstalk**

VTF crosstalk is defined as the power sum of the ratios of the aggressor Receiver voltage to the source voltage. 19 aggressors are included in the calculation. Based on crosstalk reciprocity, VTF crosstalk can be expressed as shown in Equation 5-3.

Equation 5-3.

$$XT(f) = 10\log 10 \left( \sum_{i=1}^{19} \left| \frac{V_{ai}(f)}{V_{s}(f)} \right|^{2} \right)$$

#DesignCon

(informa markets

8

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

### **Channel Spec: VTF for Advanced Package**

#### Table 5-11. Channel Characteristics

| Data Rate                       | 4-16 GT/s                                                                    | 24, 32 GT/s                                                                |

|---------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| VTF Loss (dB)                   | $L(f_N) > -3$                                                                | L(f <sub>N</sub> ) > -5                                                    |

| VTF Crosstalk (dB) <sup>a</sup> | $XT(f_{\text{N}})$ < 1.5 L(f_{\text{N}}) - 21.5 and $XT(f_{\text{N}})$ < -23 | $XT(f_{\text{N}})$ < 1.5 L(f_{\text{N}}) - 19 and $XT(f_{\text{N}})$ < -24 |

a. Based on Voltage Transfer Function Method (Tx: 25 ohm / 0.25 pF; Rx: 0.2 pF).

$f_N$  is the Nyquist frequency. The equations in the table form a segmented line in the loss-crosstalk coordinate plane, defining the pass/fail region.

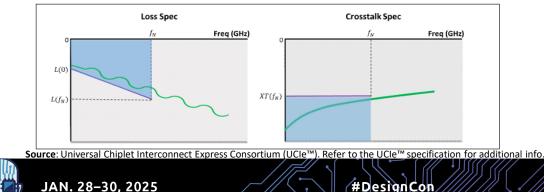

Loss and crosstalk are specified by a mask defined by the  $L(f_N)$  and  $XT(f_N)$  at Nyquist frequency. It is a linear mask from DC to  $f_N$  for loss and flat mask for crosstalk, illustrated by Figure 5-18. Loss from DC to  $f_N$  needs to be above the spec line. Crosstalk from DC to  $f_N$  needs to be below the spec line. The green line in Figure 5-18 is a representative passing signal.

(informa markets

### **Channel Spec: VTF for Standard Package**

#### 5.7.3 Standard Package

Interconnect channel should be designed with 50 ohm characteristic impedance. Insertion loss and crosstalk for requirement at Nyquist frequency with Receiver termination is defined in Table 5-18.

| Data Rate                      | 4, 8 GT/s                     | 12, 16 GT/s                   | 24, 32 GT/s                   |

|--------------------------------|-------------------------------|-------------------------------|-------------------------------|

| VTF Loss (dB) <sup>a b c</sup> | L(0) > -4.5                   | L(0) > -4.5                   | L(0) > -4.5                   |

|                                | L(f <sub>N</sub> ) > -7.5     | L(f <sub>N</sub> ) > -6.5     | $L(f_N) > -7.5$               |

| VTF Crosstalk (dB)             | $XT(f_N) < 3 * L(f_N) - 11.5$ | $XT(f_N) < 3 * L(f_N) - 11.5$ | $XT(f_N) < 2.5 * L(f_N) - 10$ |

|                                | and $XT(f_N) < -25$           | and $XT(f_N) < -25$           | and $XT(f_N) < -26$           |

Table 5-18. IL and Crosstalk for Standard Package: With Receiver Termination Enabled

a. Voltage Transfer Function for 4 GT/s and 8 GT/s (Tx: 30 ohm / 0.3pF; Rx: 50 ohm / 0.3pF).

b. Voltage Transfer Function for 12 GT/s and 16 GT/s (Tx: 30 ohm / 0.2pF; Rx: 50 ohm / 0.2pF).

c. Voltage Transfer Function for 24 GT/s and 32 GT/s (Tx: 30 ohm / 0.125pF; Rx: 50 ohm / 0.125pF).

IL and crosstalk for requirement at Nyquist frequency without Receiver termination is defined by Table 5-19. Loss and crosstalk specifications between DC and Nyquist  $f_N$  follow the same methodology defined in Section 5.7.2.1.

#### Table 5-19. IL and Crosstalk for Standard Package: No Rx Termination

| Data Rate                    | 4-12 GT/s                                                       | 16 GT/s                                                               |

|------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------------|

| VTF Loss (dB) <sup>a b</sup> | L(f <sub>N</sub> ) > -1.25                                      | L(f <sub>N</sub> ) > -1.15                                            |

| VTF Crosstalk (dB)           | $\rm XT(f_N)$ < 7 * $\rm L(f_N)$ - 12.5 and $\rm XT(f_N)$ < -15 | $XT(f_N) < 4 \ {}^{*}L(f_N) \ {}^{-}$ 13.5 and $XT(f_N) \ {}^{<} -17$ |

a. Voltage Transfer Function for 4 GT/s and 8 GT/s (Tx: 30 ohm / 0.3pF; Rx: 0.2 pF).

b. Voltage Transfer Function for 12 GT/s and 16 GT/s (Tx: 30 ohm / 0.2pF; Rx: 0.2 pF).

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

#DesignCon

10

(informa markets

### **UCle Routing/Signal Exit Order Requirement**

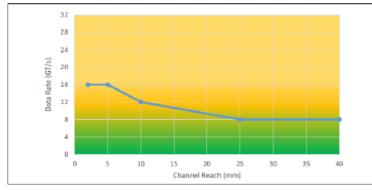

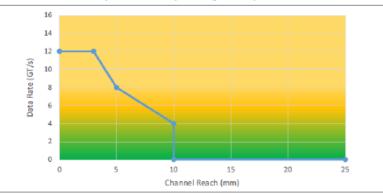

#### Maximum Channel reach for unterminated Receiver (TX swing = 0.85V)

| Data Rate<br>(GT/s) | Channel Reach<br>(mm) |

|---------------------|-----------------------|

| 16                  | 5                     |

| 12                  | 10                    |

| 8 and below         | All supported Lengths |

#### Receiver termination map for Table 5-7 (TX Swing = 0.85 V)

Receiver Termination Map for Table 5-6 (Tx Swing = 0.4 V)

#DesignCon

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

# **Compliance Kit**

#DesignCon

informa markets

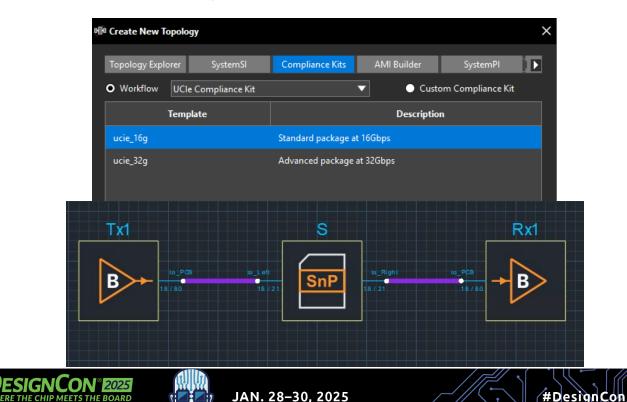

### **UCle Interface Added in Compliance Kits**

Introduced new compliance kit for UCIe<sup>™</sup> interface

Information Classification: General

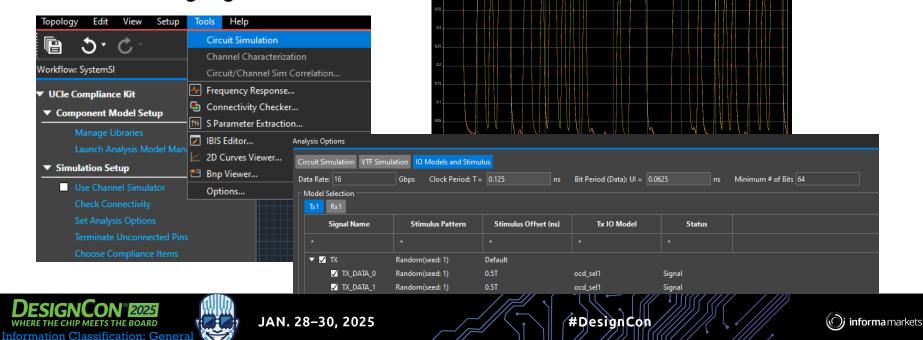

### **Details of the New UCle Kit**

- UCle<sup>™</sup> Spec v1.1

- Templates for data rates of 16 and 32Gbps

- Generic IBIS-AMI models

- Generic UCIe reference channel

- VTF calculations

- Compliance check report

### **Compliance Items**

- As required in UCIe<sup>™</sup> Spec

- Eye mask

- VTF

Analysis Options

**Circuit Simulation** Advanced Pack Standard Packa Terminations R(tx) 30

> Resolution # of Frequency P

|                                      |              |                     | -200              |                                                                            |

|--------------------------------------|--------------|---------------------|-------------------|----------------------------------------------------------------------------|

| Channel Simulation VTF Simulation IO | ) Models and | l Stimulus          | -50               | 0<br>Time (ps)                                                             |

| :kage<br>cage ✓ With Rx Termination  | Choo         | se Compliance Items |                   |                                                                            |

| ohm C(tx) 0.2 pF                     | No.          | Parameter           |                   | Values                                                                     |

| Points 128                           | Eye Dia      | gram Requirement    |                   |                                                                            |

|                                      | 1            | Eye Mask            | Eye H             | Height = 40mV, Eye Width = 0.75UI                                          |

|                                      | Voltage      | Transfer Functions  |                   |                                                                            |

|                                      | 2            | VTF Loss            |                   | L(0) > -4.5 and L(f <sub>N</sub> ) > -6.5                                  |

|                                      | 3            | VTF Crosstalk       | XT(f <sub>l</sub> | <sub>N</sub> ) < 3*L(f <sub>N</sub> ) - 11.5 and XT(f <sub>N</sub> ) < -25 |

|                                      |              |                     |                   |                                                                            |

JAN. 28-30, 2025

= 0.75UI

200

100

-100

Voltage (mV)

#DesignCon

~

✓

### **Compliance Checking**

Spec-based measurements

#### UCIe Compliance Report

Generated by Topology Workbench, Cadence Design Systems Inc., Aug 14, 2024

#### **Useful Links**

Cadence website: <u>http://www.cadence.com</u>

#### General Information

- Project File: new\_test.topx

- Circuit Simulator: SPDSIM

#### **Summary of Results**

This report shows the results of the compliance testing using Cadence TopXp. The channel simulated violates one or more compliance requirements.

#### **Eye Diagram Requirement**

WHERE THE CHIP MEETS THE BOARD Information Classification: General

| Item                       | Value                                     | Simulation Results | Pass/Fail |

|----------------------------|-------------------------------------------|--------------------|-----------|

| Eye Mask                   | Eye Height = 40mV, Eye Width = 0.75UI     | Eye Mask           |           |

| Voltage Transfer Functions | 5<br>                                     |                    |           |

| Item                       | Value                                     | Simulation Results | Pass/Fail |

| Item                       |                                           |                    |           |

| VTF Loss                   | L(0) > -4.5 and L(f <sub>N</sub> ) > -6.5 |                    |           |

JAN. 28-30, 2025

### **Running Transient Simulation (Circuit Simulation)**

- You can directly run circuit simulation in the UCIe<sup>™</sup> Compliance Kit flow

- Checking signal and crosstalk

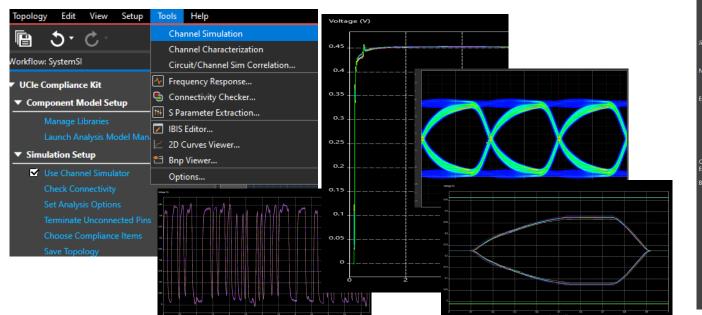

### **Running Channel Simulation**

You can run full channel simulation in the UCIe<sup>™</sup> Compliance Kit flow

| Channel Report                                                                                                                                |                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| hu Nov 28 17:30:30 2024                                                                                                                       |                                                                                                                                                                                                                           |

| eneral:                                                                                                                                       |                                                                                                                                                                                                                           |

| Number of Eye Bits<br>Ignore Bits = 8<br>Channel Coding<br>Primary Driver =<br>Data Pattern =                                                 | = Time Domain<br>16 Gbps<br>= 97ps<br>= 1332<br>396<br>5 K1_TX_DATA_0<br>random<br>= 17<br>= C<\Users\zhenm\OneDrive - Cadence Design<br>= Ecvlosers\zhenm\OneDrive - Cadence Design<br>= Even Mode Ramp Characterization |

| tter Inputs:                                                                                                                                  |                                                                                                                                                                                                                           |

| Random Jitter =                                                                                                                               | : 1%                                                                                                                                                                                                                      |

| loise Inputs:                                                                                                                                 |                                                                                                                                                                                                                           |

| Random Noise                                                                                                                                  | = 1 mV                                                                                                                                                                                                                    |

| ye Contour Measurements:                                                                                                                      |                                                                                                                                                                                                                           |

| Eye Height =<br>Eye Height Measured at<br>Eye Jitter = 0.0.<br>Eye Jitter Measured at<br>Eye Norm Jitter and Noise<br>Channel Operating Margi | 03 UI<br>= 225 mV<br>: (NJN) = 0.49                                                                                                                                                                                       |

| hannel Operating Margin (C<br>ye Density Signal to Noise Ra                                                                                   | OM) at BER 1e-16 = 14.11 dB<br>tio (SNR) = 105.30                                                                                                                                                                         |

| ER Measurements:                                                                                                                              |                                                                                                                                                                                                                           |

| -17<br>-16<br>-15<br>-14<br>-13<br>-12<br>-11<br>-10<br>-9<br>-8<br>-7<br>-6<br>-5                                                            | Eye Width(UI)<br>0.78<br>0.79<br>0.80<br>0.80<br>0.81<br>0.82<br>0.82<br>0.82<br>0.83<br>0.84<br>0.85<br>0.84<br>0.85<br>0.84<br>0.85<br>0.86<br>0.87<br>0.88<br>0.88<br>0.88                                             |

JAN. 28-30, 2025

# **Case Study**

////////#

informa markets

### **UCle Chiplets and Packaging**

#### UCle–Chiplets Integration Challenges

- Complex Die-2-Die routes (Signal, Power)

- Maintain Signal Exit orders at the beach front (die edge), while maintaining strict skew matching (lane-2-lane, lane-2-forwarded clocks,...)

- Meet SI /PI budget for channel to ensure overall End-2-End (Interconnected die) performance requirements.

- Mix of AP, SP PHYs, Term/Unterminated routes, varying die-2-die spacing, Performance in High/Low Swing modes.

- VTF based channel analysis.

#### Need for UCle-Centric Packaging Solutions

- A toolkit for Automating Package designs for UCIe based chiplet integration.

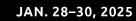

#### A Package Composed of CPU Dies, Accelerator Die(s), and I/O Tile Die Connected through UCIe

JAN. 28–30, 2025

#DesignCon

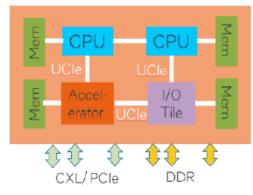

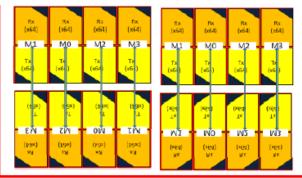

### **Chiplet Package Design – Die Placement/Routing**

- Placement

- Multiple chiplet instantiations UCIe-SP, UCIe-AP

- Orientation and alignments

- Import models

- Physical

- IBIS

- Rdie, Cdie, .pdn, current die model (.cdm)

- Choose channel (from PDK library)

- Organic

- CoWoS-S/R/L

- Bridge interposer

- ...

JAN. 28–30, 2025

#DesignCon

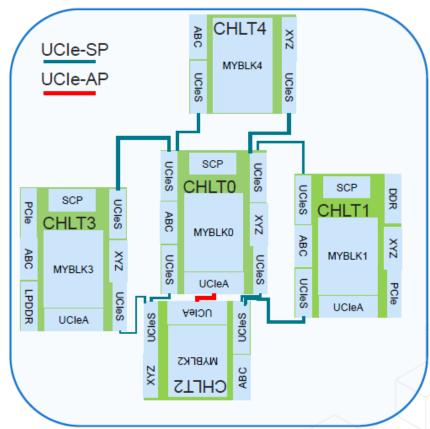

### **UCle Routing/Signal Exit Order Requirements**

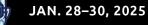

Figure 5-41. Standard Package x16 interface: Signal exit order

| Layer 1  | TX     | 0 | 1     | 2 | з | trk | vid | 12    | 13 | 14 | 15 | 15 | 14 | 13 | 12    | vld | trk | 3 | 2 | 1     | 0 | Rx     |

|----------|--------|---|-------|---|---|-----|-----|-------|----|----|----|----|----|----|-------|-----|-----|---|---|-------|---|--------|

| Layer 2  | Module | 4 | 5     | 6 | 7 | ckp | den | 8     | 0  | 10 | 11 | 11 | 10 | 0  | 8     | ckn | dep | 7 | 6 | 5     | 4 | Module |

| Sideband |        | t | datas | b |   |     | 1   | xckst |    |    |    |    |    |    | xdest |     |     |   | D | datas | b |        |

Figure 5-44. Standard Package cross section for stacked module

#### Figure 5-43. Standard Package x32 interface: Signal exit routing

| Layer 1                    | Tx       | 0  | 1     | 2   | 3  | trk   | vid | 12  | 13    | 14  | 15    | 15  | 14    | 13   | 12  | vid | trk   | 3   | 2   | 1      | 0   | Rx      |

|----------------------------|----------|----|-------|-----|----|-------|-----|-----|-------|-----|-------|-----|-------|------|-----|-----|-------|-----|-----|--------|-----|---------|

| Layer 2                    | Module 1 | 4  | 5     | 6   | 7  | dkp   | din | 8   | 9     | 10  | 11    | 11  | 10    | 9    | 8   | den | dep   | 7   | 6   | 5      | -4  | Module  |

| Layer2<br>Layer3<br>Layer4 | Rx       | 0  | 1     | 2   | 3  | trk   | vid | 12  | 13    | 14  | 15    | 15  | 14    | 13   | 12  | vid | trk   | 3   | 2   | 1      | 0   | Τx      |

| Layer 4                    | Module 2 | 4  | 5     | 6   | 7  | dkp   | din | 8   | 9     | 10  | 11    | 11  | 10    | 9    | 8   | dim | dkp   | 7   | 6   | 5      | 4   | Module  |

| Sideband                   |          | m1 | txdat | asb | m2 | nidat | asb | mit | icksb | m2n | tcksb | m2b | cdesb | m1rx | dab | m2  | txdat | asb | _m1 | nedati | asb | Sidebar |

Source: Universal Chiplet Interconnect Express Consortium (UCle™). Refer to the UCle™ specification for additional info.

#DesignCon

### **UCle AP Interposer Design Requirements**

Figure 5-23 shows the signal exit order for the 10-column x64 Advanced Package bump map.

|          | Left to Right |                 |           |          |           |          |           |          |           |          |          |           |           |            |             |            |     |

|----------|---------------|-----------------|-----------|----------|-----------|----------|-----------|----------|-----------|----------|----------|-----------|-----------|------------|-------------|------------|-----|

|          |               | <b>5/4/4/00</b> | bidata0   | tolatal  | todata2   | todata3  | bdata4    | bidataS  | tolatal   | trata7   | todat a8 | bdata9    | txdata30  | b detail   | todatal2    | Didata D   | C)  |

| Tx       | Cont          | tolata14        | todata15  | todata15 | bdata17   | todata18 | todata 19 | tedata20 | todata21  | tadata22 | bdata13  | txdata14  | txdata25  | b data25   | todata27    | bdata28    | Cor |

| Braikout | Conti         | tolat29         | todata30  | tida alt | tola A01  | tx880    | tukn      | tukp     | M/A       | tivid    | twidRD   | todauA02  | todat #32 | B data 38  | todata34    | bdata35    | Cor |

|          | Cont2         | todata36        | todata37  | Esdata38 | bdata39   | todata40 | todata41  | txdata42 | todata43  | tadata44 | bdata45  | tx:8/1246 | todat #47 | to data48  | todata48    | bdata50    | Cor |

|          | ContB         | tolati51        | todata 92 | todata63 | bdata54   | todata65 | todata 96 | todata57 | todata58  | todata59 | Detailed | 0.04061   | wdat #62  | to data 69 | to data RDB |            |     |

|          | Left to Hight |                 |           |          |           |          |           |          |           |          |          |           |           |            |             |            |     |

|          |               | rodata ROS      | m data63  | rodata62 | odataśi   | rxdata60 | rodata 99 | rxdata58 | ndata57   | radata56 | odata55  | ndata64   | rodatu53  | redata52   | rod#451     | ordata50   | Ca  |

| Rx       | Cont          | relate/9        | m data 48 | radata47 | odata46   | rodata45 | rodata44  | redata43 | ndata/2   | radata41 | odata40  | ndata39   | redata38  | redata37   | rodata36    | ordata35   | Con |

| Breakout | Conti         | relate34        | m data33  | rodata32 | ridataR02 | ov/d0    | on M      | rxtrk    | radip     | ocin     | nukRD    | rodataR01 | red:sta31 | redata30   | rodata29    | sida ta 28 | Con |

|          | Cont2         | redat/27        | mdata26   | rodata25 | Ndita34   | rodata13 | redata 32 | redata21 | ndata20   | radata19 | odata18  | ndata17   | redata16  | rodata15   | rodata14    | ordata13   | Con |

|          | ContB         | redatat2        | redata11  | rodata10 | redata9   | rodat a8 | odata7    | ndata6   | codat als | rolats4  | redata3  | ordata2   | rodatat   | reduita 0  | metata 800  |            |     |

#### Figure 5-23. 10-column x64 Advanced Package Bump map: Signal exit order

UCIe standard allocates 25% UI of jitter to channel related degradation (loss+xtalk)

- After UCIe data channels are designed on the interposer, the resulting design should be verified with circuit level simulations

- With an ideal driver and receiver circuit, using the interposer channel, the eye should have ≥ 75% UI horizontal opening and ≥ 40mV vertical height

- Example: at 16Gbps, channel related jitter (xtalk+loss) should be ≤ 15.6ps

- UCIe is sensitive to supply noise, recommend keeping the UCIe PHY supplies separate than the SoC supplies

- The AP UCIe PHY was designed with the assumption that there is a total of 50 mVpp supply noise, where 20-25mVpp of that being allocated to the IP.

- Using the die model for the IP in conjunction with the extracted interposer and package s-parameter models, the target should be that the supply noise be less than 25mVpp. Higher noise values will need to be evaluated on a case-by-case basis.

- Additionally, the IR drop across the interposer power routings should be minimized. We should target this drop to be less than 5mV, but there is some flexibility this depending on the domain

#DesignCon

23

informa markets

### GUI-Based Link Connectivity

- Fixed signal connectivity between Die modules [ link\_AP.v, link\_sp.v].

- Connect the Dies/ Links through Verilog File Placement in GUI. Validated Connectivity by Construction.

- Die placements / orientation ( Die Rotate, Mirrored Die Rotate, Multi Modules)

- · Complete non-Die2-Die , Power Rail connectivity.

| Die 0    | Link SP | Die 1    | Die 0    | Link SP | Die 1    |

|----------|---------|----------|----------|---------|----------|

| txclkp   | -       | rxclkp   | rxclkp   |         | txclkp   |

| txclkn   | -       | rxclkn   | rxclkn   | •       | txclkn   |

| txdata0  | -       | rxdata0  | rxdata0  |         | txdata0  |

| txdata1  | -       | rxdata1  | rxdata1  | -       | txdata1  |

| txdata2  | -       | rxdata2  | rxdata2  | •       | txdata2  |

| txdata3  | -       | rxdata3  | rxdata3  |         | txdata3  |

| txdata4  | -       | rxdata4  | rxdata4  |         | txdata4  |

| txdata5  | •       | rxdata5  | rxdata5  | -       | txdata5  |

| txdata6  | 1       | rxdata6  | rxdata6  | -       | txdata6  |

| txdata7  | •       | rxdata7  | rxdata7  | •       | txdata7  |

| txdata8  | -       | rxdata8  | rxdata8  | -       | txdata8  |

| txdata9  |         | rxdata9  | rxdata9  | •       | txdata9  |

| txdata10 | -       | rxdata10 | rxdata10 |         | txdata10 |

| txdata11 |         | rxdata11 | rxdata11 |         | txdata11 |

| txdata12 | -       | rxdata12 | rxdata12 | -       | txdata12 |

| txdata13 | •       | rxdata13 | rxdata13 |         | txdata13 |

| txdata14 |         | rxdata14 | rxdata14 |         | txdata14 |

| txdata15 | 1       | rxdata15 | rxdata15 | -       | txdata15 |

| txvld    | •       | rxvld    | rxvld    |         | txvld    |

| txtrk    | 1       | rxtrk    | rxtrk    | •       | txtrk    |

| txdatasb |         | rxdatasb | rxdatasb |         | txdatasb |

| txclksb  |         | rxclksb  | rxclksb  |         | txclksb  |

|  | Die 0       | Link AP | Die 1      | Die 0      | Link AP    | Die 1      |  |  |  |  |

|--|-------------|---------|------------|------------|------------|------------|--|--|--|--|

|  | txclkp      |         | rxclkp     | rxclkp     | •          | txclkp     |  |  |  |  |

|  | txclkn      |         | rxclkn     | rxclkn     | •          | txclkn     |  |  |  |  |

|  | txdata0     |         | rxdata0    | rxdata0    | •          | txdata0    |  |  |  |  |

|  | txdata1     | •       | rxdata1    | rxdata1    | •          | txdata1    |  |  |  |  |

|  | txdata2     |         | rxdata2    | rxdata2    | •          | txdata2    |  |  |  |  |

|  | txdata3     |         | rxdata3    | rxdata3    | 4          | txdata3    |  |  |  |  |

|  | txdata4     |         | rxdata4    | rxdata4    | •          | txdata4    |  |  |  |  |

|  | txdata5     |         | rxdata5    | rxdata5    | •          | txdata5    |  |  |  |  |

|  |             |         |            |            | •          |            |  |  |  |  |

|  |             |         |            |            | •          |            |  |  |  |  |

|  |             |         |            |            |            |            |  |  |  |  |

|  |             |         |            |            |            |            |  |  |  |  |

|  | txdata58    |         | rxdata58   | txdata58   |            | rxdata58   |  |  |  |  |

|  | txdata59    |         | rxdata59   | txdata59   | •          | rxdata59   |  |  |  |  |

|  | txdata60    |         | rxdata60   | txdata60   | -          | rxdata60   |  |  |  |  |

|  | txdata61    |         | rxdata61   | txdata61   | •          | rxdata61   |  |  |  |  |

|  | txdata62    |         | rxdata62   | txdata62   |            | rxdata62   |  |  |  |  |

|  | txdata63    |         | rxdata63   | txdata63   |            | rxdata63   |  |  |  |  |

|  | txvld       |         | rxvld      | rxvld      | •          | txvld      |  |  |  |  |

|  | txtrk       |         | rxtrk      | rxtrk      |            | txtrk      |  |  |  |  |

|  |             |         |            |            |            |            |  |  |  |  |

|  | txdataRD0   |         | rxdataRD0  | rxdataRD0  |            | txdataRD0  |  |  |  |  |

|  | txdataRD1   |         | rxdataRD1  | rxdataRD1  |            | txdataRD1  |  |  |  |  |

|  | txdataRD2   |         | rxdataRD2  | rxdataRD2  |            | txdataRD2  |  |  |  |  |

|  | txdataRD3   |         | rxdataRD3  | rxdataRD3  | ←          | txdataRD3  |  |  |  |  |

|  | txvldRD     |         | rxvIdRD    | rxvldRD    | ←          | txvldRD    |  |  |  |  |

|  | txtrkRD     |         | rtrkRD     | rtrkRD     | -          | txtrkRD    |  |  |  |  |

|  | txdatasb    |         | rxdatasb   | rxdatasb   | <b>—</b> — | txdatasb   |  |  |  |  |

|  | txclksb     |         | rxclksb    | rxclksb    | •          | txclksb    |  |  |  |  |

|  | txdatasbRD  |         | rxdatasbRD | rxdatasbRI | D          | txdatasbRD |  |  |  |  |

|  | txclksbRD - |         | rxclksbRD  | rxclksbRD  |            | txclksbRD  |  |  |  |  |

JAN. 28–30, 2025

#DesignCon

### **Blizzard N7 SP – Package Overview**

# SP - Routing (16mm average) Samples and Matching Lane Skews

|    |         |                | (mm)  | (ps)  | delta |      |

|----|---------|----------------|-------|-------|-------|------|

| 1  | Layer 6 | RXCKSB_M0_AB   | 16.83 | 89.04 | 0.1   |      |

| 2  | Layer o | RXDATASB_M0_AB | 16.81 | 88.94 | 0.1   |      |

| 3  | Layer 4 | RXDATA10_M0_AB | 16.27 | 84.34 | 0.38  | 3.84 |

| 4  |         | RXDATA6_M0_AB  | 16.25 | 84.24 |       |      |

| 5  |         | RXDATA5_M0_AB  | 16.24 | 84.2  |       |      |

| 6  |         | RXDATA11_M0_AB | 16.24 | 84.19 |       |      |

| 7  |         | RXDATA9_M0_AB  | 16.23 | 84.15 |       |      |

| 8  |         | RXDATA7_M0_AB  | 16.23 | 84.12 |       |      |

| 9  |         | RXDATA4_M0_AB  | 16.22 | 84.07 |       |      |

| 10 |         | RXDATA8_M0_AB  | 16.22 | 84.06 |       |      |

| 11 |         | RXCKN_M0_AB    | 16.20 | 83.96 |       |      |

| 12 |         | RXCKP_M0_AB    | 16.20 | 83.96 |       |      |

| 13 | Layer 2 | RXDATA0_M0_AB  | 15.98 | 80.63 | 0.13  |      |

| 14 |         | RXDATA14_M0_AB | 15.98 | 80.61 |       |      |

| 15 |         | RXDATA12_M0_AB | 15.98 | 80.61 |       |      |

| 16 |         | RXDATA3_M0_AB  | 15.97 | 80.61 |       |      |

| 17 |         | RXDATA13_M0_AB | 15.97 | 80.6  |       |      |

| 18 |         | RXVLD_M0_AB    | 15.97 | 80.58 |       |      |

| 19 |         | RXDATA1_M0_AB  | 15.97 | 80.58 |       |      |

| 20 |         | RXTRK_M0_AB    | 15.97 | 80.58 |       |      |

| 21 |         | RXDATA2_M0_AB  | 15.96 | 80.56 |       |      |

| 22 |         | RXDATA15_M0_AB | 15.96 | 80.5  |       |      |

- 16 x 2 32 ports for Rx to Tx Data lanes

- 4 x 2 8 ports for Clock, TRK & VLD

- 7 x 2 14 ports for VDD Core Power.

cādence

7 JAN. 28–30, 2025

#DesignCon/

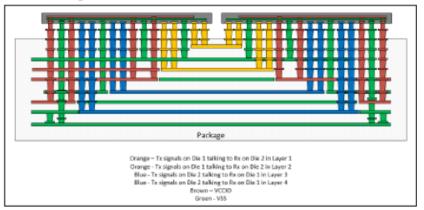

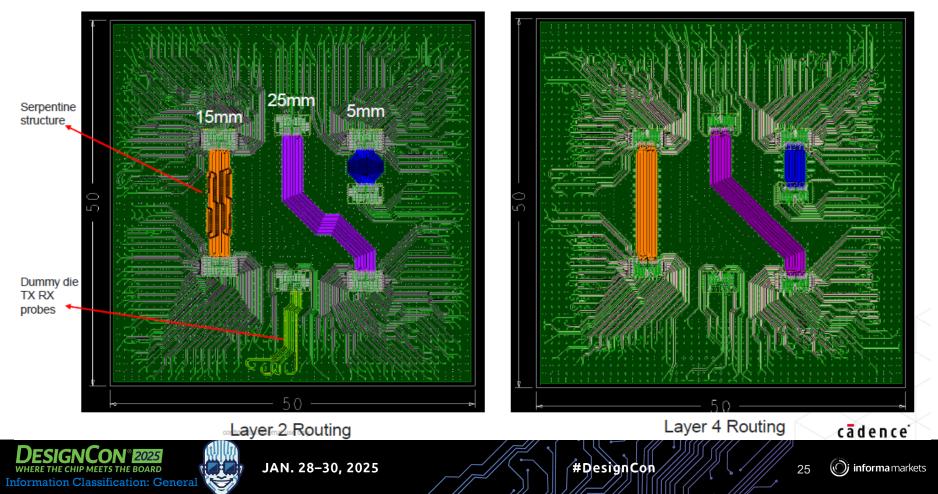

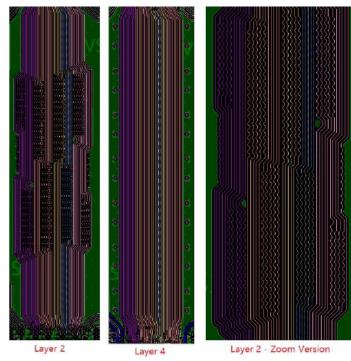

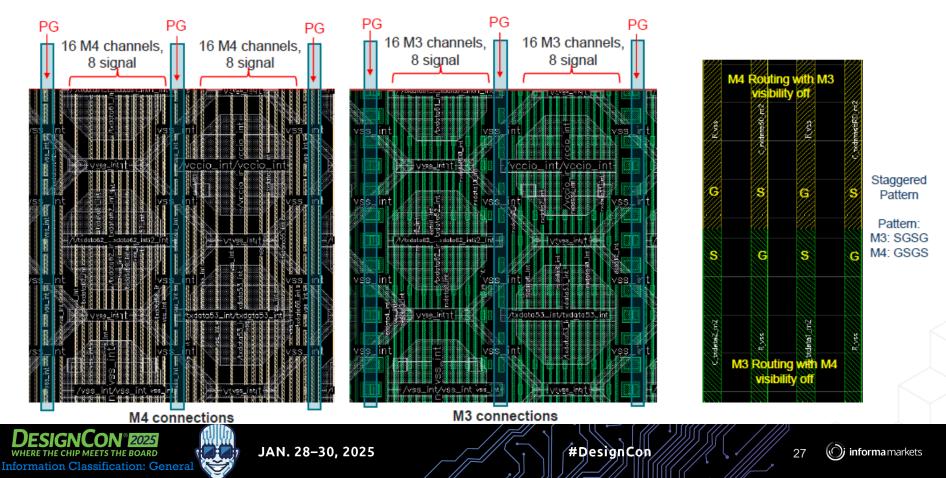

### M4 – M3 Metal Connections – Sample – CoWos\_S

### **Die2Die Route - Samples**

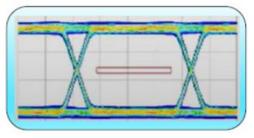

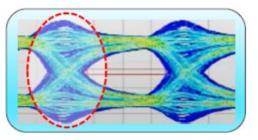

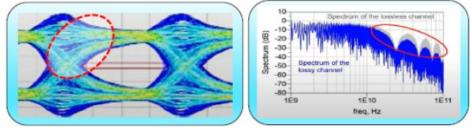

Simulate noiseless, jitter-less behavioral Tx and Rx models for ideal eye mask at receiver

Thick eye level – Near-end crosstalk – Traces are closer

Far-end crosstalk – closes Rx eye undershoot/overshoot

28

() informa markets

Simulate noiseless, jitter-less behavioral Tx and Rx models for ideal eye mask at receiver

#### Optimize trace spacing – to meet UCIe<sup>™</sup> VTF crosstalk specification, open the eye (meet eye mask spec)

#DesignCon

### **Die2Die Signal Integrity Checks**

- Simulate noiseless, jitter-less behavioral Tx and Rx models for ideal eye mask compliance at receiver

- To optimize the channel routes

- Channel crosstalk, jitter analysis

- Frequency-dependent loss (Tx and Rx channels)

- Analysis conditions:

- Rx eye analysis for terminated/unterminated use cases SP

- AP links unterminated

- Analysis with 45 Ohms < Rx termination < 55 Ohms

- $_{\circ}$  0.4V < Tx swing < 0.85V

- Support for all supported data rates

- Support for IP Process corners

- Forwarded Rx clock phases: (90, 270), (45, 135)

- Signal analysis methods

- Tx eye diagram analysis

- VTF loss (for channel)

JAN. 28–30, 2025

\ ///

29

#DesignCon

() informa markets

# UCle Toolkit Flow (Package Design, Analysis, Release)

UCle<sup>™</sup> Compliance Design Toolkit with a GUI front end for:

- Chiplet design import, placement

- Substrate/interposer PDK import

- Chiplet signal interconnects, package I/O connectivity

- Power domain design

- Lossless channel simulation for signal route strategies

3D – Extraction/S-parameter model generation VTF model creation Automated flow from routing>extraction>SI/PI Iterate fixes, extraction, and SI analysis for review Through meeting the Link requirement

Design/analysis interations to automate the toolkit

#DesignCon

# Demo

# Please visit the Cadence Booth #827 for a Live Demo of the UCIe Compliance Kit

JAN. 28–30, 2025

#DesignCon